3. Evoluzione delle SDRAM: dalle DDR3 alle DDR4 - Parte seconda

I/O Interface

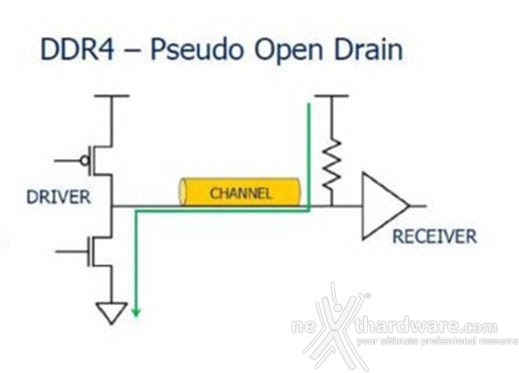

Le DDR4 utilizzano una interfaccia di I/O che fa uso di una nuova connessione di tipo Pseudo-Open Drain 1,2V (POD12) rispetto a quella standard, di tipo Push-Pull, adottata nelle DDR3.

Questa interfaccia, facente parte delle specifiche JEDEC, pur essendo nuova alla famiglia delle SDRAM, è già stata brillantemente collaudata sulle GDDR5, le quali operano spesso a frequenze più elevate rispetto a quanto previsto per le DDR4.

Uno schema di I/O così evoluto aiuta a mantenere l'integrità del segnale, permettendo, al contempo, velocità di trasmissione più elevate e consentendo l'adozione di tanto innovative quanto efficaci modalità di risparmio energetico.

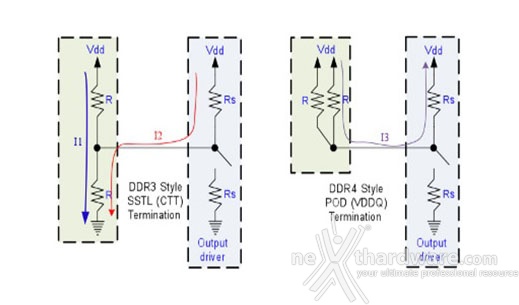

Nei seguenti diagrammi si possono intravedere le differenze a livello elettrico del segnale utilizzato nelle DDR3 (a sinistra) comparato a quello adottato nelle DDR4.

Fig.5 Schema segnale elettrico DDR3 vs DDR4

Come possiamo notare, il segnale elettrico dell'interfaccia di I/O cambia dal Series-Stub Terminated Logic (SSTL) utilizzato sulle DDR3, allo Pseudo-Open Drain (POD) delle DDR4.

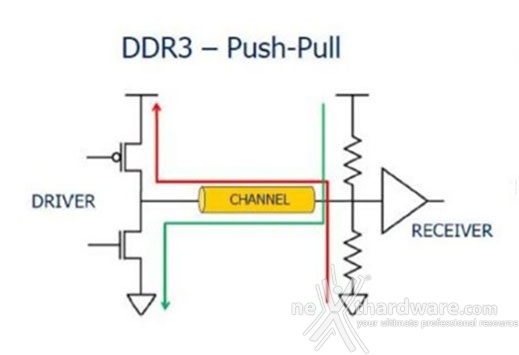

Nel circuito SSTL15 delle DDR3, che opera in modalità Push-Pull, si veniva a creare la necessità di utilizzo di due distinte correnti elettriche: la prima (l1), fungente da corrente di terminazione, mentre la seconda (l2), atta a pilotare il segnale "high" attraverso il circuito stesso.

Fig.6 Modalità Push-Pull DDR3

Nella tipologia di circuito POD del quale usufruiscono le DDR4, non è invece necessaria alcuna energia al fine di pilotare il segnale "high" all'interno dello stesso circuito, permettendo così a questa nuova generazione di SDRAM di ridurre in misura sensibile i requisiti di alimentazione.

Fig.7 Modalità Pseudo Open Drain DDR4

Error Detection

I dispositivi che operano ad una più alta frequenza di clock rendono tipicamente possibile la trasmissione di una maggiore quantità di dati in un dato periodo di tempo.

Utilizzare però frequenze più elevate dà luogo, al contempo, ad una maggiore complessità nelle operazioni di trasmissione e ricezione delle informazioni veicolate che, a loro volta, possono generare disturbi indesiderati e deleteri nel segnale.

A volte i disturbi sono tali da portare, sostanzialmente, alla variazione del tutto spontanea di alcuni bit nelle fasi di scrittura.

Per risolvere questi possibili inconvenienti le DDR4, in particolare, offrono due modalità di rilevazione degli errori, ovvero il controllo della ridondanza (CRC) durante il trasferimento dei dati ed il controllo di parità nelle operazioni relative ai comandi e l'indirizzamento dei bit, nonché il Data Bus Inversion (DBI), per gestire in maniera efficiente il mantenimento dell'integrità del segnale e, nel contempo, conseguire una drastica riduzione del consumo energetico.

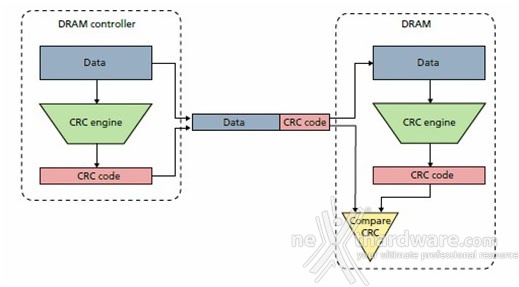

CRC Error Detection

Tramite il CRC, adottato in seno allo standard nelle specifiche primarie DDR4 (sulle DDR3 era data la possibilità di implementarlo, invece, opzionalmente), vengono fornite capacità di individuazione in tempo reale degli errori verificati sul bus di comunicazione dei dati, migliorando in maniera sostanziale l'affidabilità dell'intero sistema di trasferimento delle informazioni in memoria durante le fasi di scrittura.

Le DDR4 presentano un sistema di controllo degli errori strutturato ad 8 bit e funzionante secondo lo schema sottostante.

Fig.8 Schema funzionamento CRC Error Detection

In breve, all'interno dello stesso DRAM controller, il motore CRC, a seguito della richiesta di trasmissione dei dati, genera una stringa di bit di controllo (CRC code) strettamente relativa a quei dati da trasmettere, spedendo insieme il tutto, dati e bit di controllo, ad ogni burst in scrittura.

Una volta che i dati giungono a destinazione all'interno dei chip di memoria DDR4, viene prodotta una seconda stringa CRC: a questo punto, quindi, i due insiemi di bit di controllo vengono comparati e, qualora non dovessero corrispondere, verrà imposto uno stato di errore.

A quel punto, i dati errati già memorizzati in memoria verranno corretti dal controller tramite la ricostruzione ottenuta a partire dalla prima stringa CRC, generata in fase di trasmissione, permettendo di risolvere l'errore.

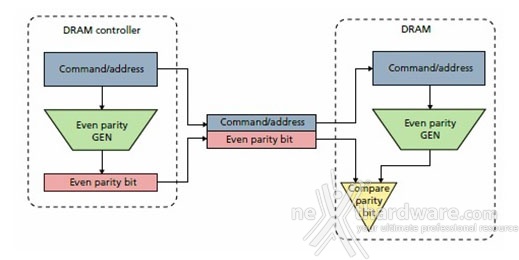

Parity Error Detection

Lo schema logico funzionale del sistema di controllo della parità è del tutto simile a quello relativo al CRC visto in precedenza, con la sostanziale differenza di operare esclusivamente sul bus dei comandi/indirizzamento.

Fig.9 Schema funzionamento Parity Error Detection

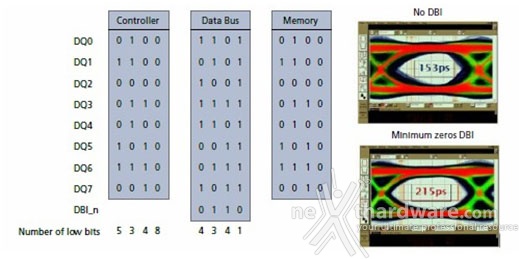

Data Bus Inversion

La funzionalità di Data Bus Inversion (DBI) è supportata unicamente sulle configurazioni DDR4 SDRAM in modalità x8 e x16: essa condivide il pin per il Data Mask (DM) nonché le funzionalità TDQS e può essere applicata in entrambe le operazioni di lettura e scrittura.

L'unico limite imposto al DBI è relativo alla fase di scrittura, specificatamente nella circostanza per cui tale funzionalità può essere applicata al TDQS, ma non contemporaneamente al Data Mask, ovvero qualora quest'ultimo risulti abilitato.

Funzionalità DBI:

- inversione opportuna dei data-bit:

- trasferimento di un minor numero di bit con valore pari a 0 (al massimo quattro bit di ogni byte, incluso quello relativo al pin DBI);

- minor consumo di energia (è necessaria solo quella dei bit con valore pari a 0);

- minore commutazione dei bit, a tutto vantaggio della pulizia del segnale in particolar modo alle alte frequenze;

- abilitazione separata delle operazioni di lettura e scrittura.

Esempio

| Lettura | Scrittura |

Se più di quattro bit facenti parte del byte da trasmettere hanno valore pari a 0 (low)

| Se il DBI ha valore 0 (low), la scrittura dei dati viene invertita

|

Se quattro o meno bit facenti parte del byte da trasmettere hanno valore pari a 0 (low)

| Se il DBI ha valore 1 (high), i dati non vengono invertiti |

Fig.10 Esempio applicazione Data Bus Inversion

Tabella riepilogativa DDR4 vs DDR3

| Feature/Option | DDR3 | DDR4 | Vantaggi DDR4 |

| Tensione | 1,5V | 1,2V | Minor esigenza di energia della memoria |

| Input Vref | 2 - DQs and CMD/ADDR | 1 - CMD/ADDR | Vrefdq interno |

| Standard "Low Voltage" | Â DDR3L a 1,35V | 1,05V | Minor consumo energetico della memoria |

| Velocità dati | Da 800MB/s a 2133MB/s | Da 1600MB/s a 3200MB/s | Migrazione a I/O più veloci |

| Densità chip | 512MB-8GB | 2GB-16GB | Capacità DIMM maggiorate |

| Banchi interni | 8 | 16 | Più banchi |

| Gruppi di banchi (BG) | 0 | 4 | Accessi di trasferimento più rapidi |

| tCK - DLL Enabled | Da 300MHz a 800MHz | Da 667MHz a 1.6GHz | Maggiore velocità dei dati |

| tCK - DLL Disabled | Da 10MHz a 125MHz | Da indefinita a 125MHz | Supporto completo DLL-off |

| Latenza di lettura | AL + CL | AL + CL | Valori estesi |

| Latenza di scrittura | AL + CWLÂ | AL + CWL | Valori estesi |

| DQ Driver (ALT) | 40 ohm | 48 ohm | Ottimizzato per applicazioni PtP |

| Bud DQ | SSTL15 | POD12 | Minor consumo e rumore I/O |

| Valori RTT in ohm | 120, 60, 40, 30, 20 | 240, 120. 80, 60, 48, 40, 34 | Supporto per maggiore velocità dei dati |

| Rtt non consentito | READ bursts |  disattivato durante READ bursts | Facilità d'uso |

| Modalità ODT | Nominale, Dinamica | Nominale, Dinamica, Park | Modalità di controllo aggiuntiva; modalità valori OTF |

| Controllo ODT | Signaling ODT necessario | Signaling ODT non necessario | Controllo ODT semplificato; supporto Non-ODT routing, PtP App |

| Registro multifunzione (MPR) | Quattro registri - 1 definito, 3 RFU | Quattro registri - 3 definiti, 1 RFU | Ulteriori opzioni di readout |

| Tipi DIMM | RDIMM, LRDIMM, UDIMM, SODIMM | RDIMM, LRDIMM, UDIMM, SODIMM | |

| Pin DIMM | 240 (R, LR, U); 204 (SODIMM) | 288 (R, LR, U); 260 (SODIMM) | |

| RAS | ECC | CRC, Parity, Addressability, GDM | Ulteriori funzioni RAS; maggiore integrità di dati |