4. Front End, Physical Register File e Execution Cluster

Â

Front End

Â

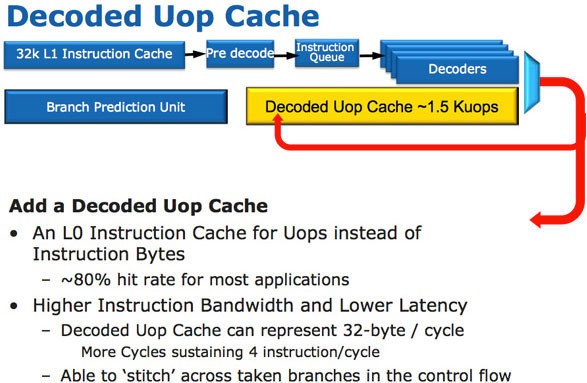

La gestione del Front End delle CPU Intel ha avuto un notevole miglioramento con lâintroduzione del Loop Stream Detector (LSD) nelle CPU Intel Core 2, componente che può rilevare lâesecuzione di un ciclo in un software, disattivare automaticamente la logica dedicata al branch prediction e le unità di fetch e decode, al fine di risparmiare energia. In Sandy Bridge è stata aggiunta una cache dedicata alle micro-op, chiamata Decoded Uop Cache, che si occupa di memorizzare le prossime operazioni da eseguire disattivando tutte le unità non più necessarie. Questa cache può essere considerata di livello 0 e contiene circa 1500 micro-ops, secondo fonte Intel, e dovrebbe coprire lâ80% delle operazioni normalmente eseguite dalle applicazioni, migliorando di fatto la latenza e limitando gli accessi agli altri livelli di cache e memoria.

Â

A differenza di quanto implementato nelle CPU Pentium 4, la Decoded Uop Cache non memorizza la âstoriaâ delle istruzioni eseguite, ma le istruzioni vere e proprie, replicando questa informazione,a sua volta, nella cache di livello 1.

Â

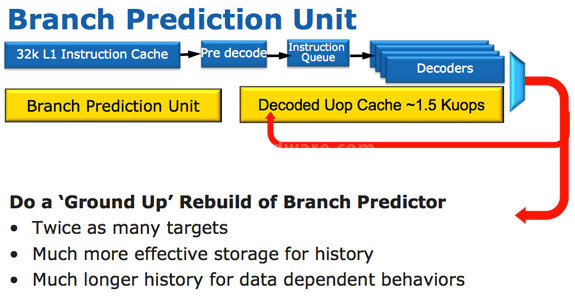

Altra importante novità è lâintroduzione di una nuova Branch Prediction Unit, che riesce a prevedere in modo più efficiente quale sarà la prossima operazione da eseguire, al fine di migliorare il carico della CPU e limitare gli accessi agli altri componenti, memoria in primis. Sandy Bridge mantiene inoltre una history più lunga delle operazioni eseguite, in modo da eseguire un confronto più accurato con le previsioni fatte.

Â

Physical Register File e Execution Cluster

Â

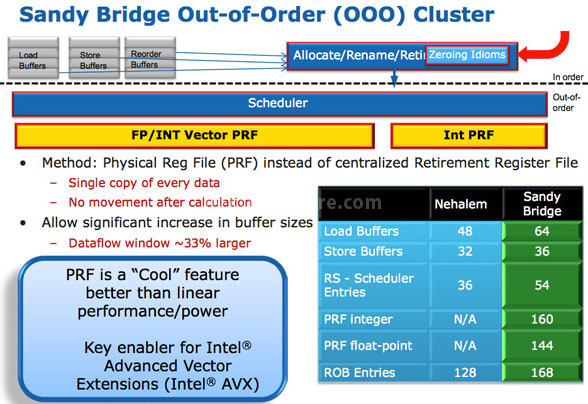

Al pari di AMD, anche Intel ha deciso di utilizzare per le sue nuove CPU un Physical Register File che consente di mappare tutte le operazioni in registi e puntare di volta in volta a questi, senza dover eseguire copie che risulatno particolarmente esose in termini energetici e prestazionali.

Â

Â

Questa modifica è stata resa necessaria anche per migliorare la velocità di esecuzione delle istruzioni AVX (Advanced Vector Extensions), che supportano operandi a 256-bit e che avrebbero avuto bisogno di un elevato bandwitch per poter lavorare correttamente.

Â

Â

LâExecution Cluster di Sandy Bridge differisce da quello di Nehalem perché utilizza un numero maggiore di unità condivise e consente l'esecuzione di operazioni a 256-bit, utilizzando due stack a 128 bit, senza la necessità di duplicare parte della circuiteria e raddoppiando di fatto i FLOPs. Diretta conseguenza della modifica degli Execution Cluster, è una massiccia riorganizzazione del Memory Cluster, che deve riuscire a fornire un numero doppio di dati per poter gestire le nuove istruzioni al doppio della velocità di elaborazione.

Â

Â