2. 3D Vertical NAND

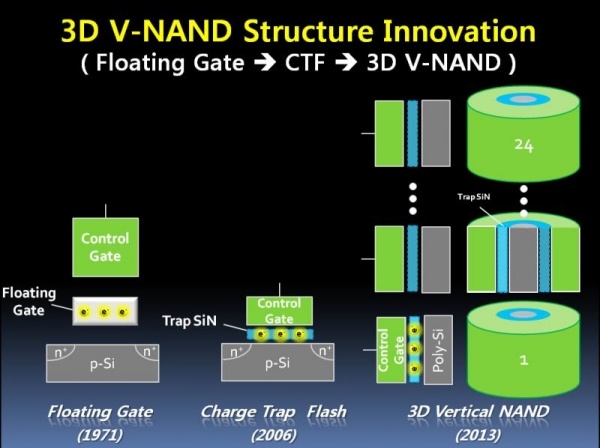

Procedendo in questi ultimi anni nelle sviluppo di soluzioni più efficienti, due sono state le grandi problematiche riscontrate dai produttori nel tentativo di procedere nella naturale evoluzione delle NAND Flash, una volta raggiunta una tecnologia costruttiva estremamente ridotta (2xnm).

La prima è rappresentata dalle grandi difficoltà nel raggiungimento di uno scaling ancora più ridotto ma contestualmente efficiente nelle due dimensioni, lunghezza e larghezza, della superficie del die.

Mentre per quanto riguarda la seconda difficoltà , il limite è invece costituito dal numero troppo esiguo di elettroni gestibili, a quelle dimensioni, per mantenere coerenti ed efficaci le funzionalità di una cella di memoria NAND.

Figura 12: evoluzione tecnologica delle celle NAND (fonte Samsung)

Partendo da questi limiti e alla ricerca di una valida ed efficace soluzione, Toshiba giunse ad inventare e sviluppare qualche tempo fa, le prime NAND 3D: questa evoluzione è stata così innovativa e promettente nel settore, da essere già nell'immediatezza identificata come la strada giusta da percorrere nel futuro, anche da altri grandi protagonisti del settore come Samsung.

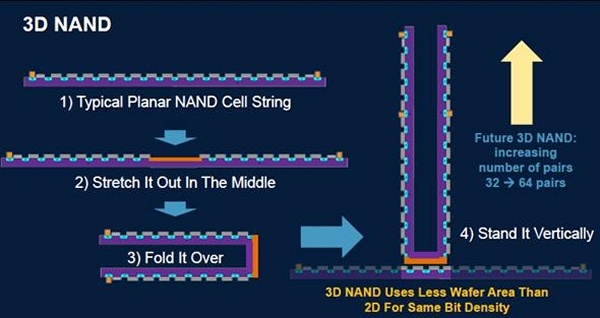

L'idea concettualmente alla base è davvero semplice ma allo stesso tempo geniale: a partire dall'ipotetica e lunga stringa longitudinale che ospita le celle di memoria Flash NAND standard, è utile creare uno spazio privo di celle al centro, in modo da dividere la stringa in due rami di ugual misura con una giusta base di appoggio.

A questo punto occorre piegare un ramo verso l'altro fino a renderli paralleli e dislocarli in maniera verticale.

Figura 13: ideazione e sviluppo di una cella NAND 3D Vertical (fonte Samsung)

Con lo stesso procedimento, vengono così disposte tutta una serie di doppie stringhe ottenute in modo analogo: queste possono essere infine impilate alla base su una nuova stringa principale, planare, che ne estende le connessioni con le relative celle e soprattutto in grado di prenderne a livello elettrico il controllo.

Entrando in qualche modo nel dettaglio, una serie di innovazioni e nuove tecnologie sono divenute artefici dell'ottenimento del risultato voluto, in quanto continuando a congegnare i gate alla vecchia maniera, il sistema semplicemente non avrebbe avuto modo di funzionare.

Gli ingegneri Toshiba pensarono bene di ideare una duplice strategia: una prima fu adottata per l'implementazione della stringa planare, del tutto semplificata rispetto al passato, e una seconda, completamente differente, fu destinata a quella verticale.

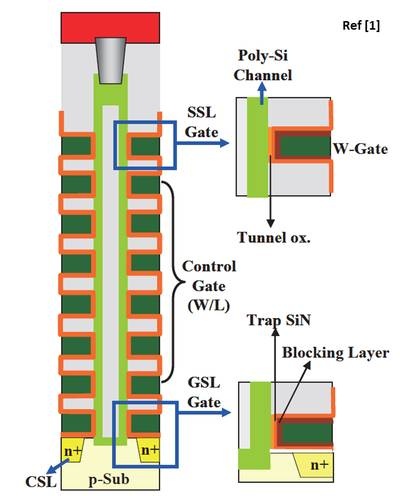

Figura 14: schema dello stack di una cella 3D Vertical NAND (fonte Samsung)

Bisogna innanzitutto chiarire che il processo costruttivo col quale vengono prodotte le stringhe verticali, con nodi dalle geometrie di ~40nm, per i motivi a cui si è accennato non può essere il medesimo usato comunemente per quelle planari.

Ma soprattutto è in realtà impossibile ripiegare una stringa di celle NAND, per come la conosciamo, senza pregiudicare a livello funzionale le caratteristiche tipiche dei transistor a doppio gate in essa contenuti: sotto l'aspetto della dislocazione verticale si erano concentrate purtroppo alcune difficoltà mai affrontate prima.

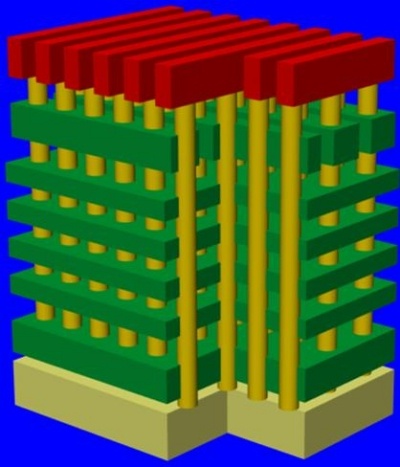

Figura 15: rappresentazione tridimensionale di un array V-NAND

In sostanza tali difficoltà derivano da un assoluto punto fermo, l'impossibilità cioè di usare per questa soluzione il procedimento litografico standard: la luce infatti non può, tramite la litografia, essere gestita per costituire pattern a sviluppo verticale, pertanto l'idea di mutuare una sorta di duplicazione degli ormai collaudati gate flottanti, non poteva in alcun modo esser presa in considerazione.

Così gli ingegneri stabilirono che sulla stringa planare 3D NAND venissero inseriti i soli gate di controllo mentre verticalmente, al posto dei vecchi flottanti, decisero invece di posizionare dei transistor composti con materiali differenti: i charge trap in Nitruro di Silicio.

La differenza tra i vecchi e i nuovi è sostanziale in quanto, contrariamente ai primi, questi ultimi sono costituiti da layer non conduttivi, ma ugualmente in grado di trattenere e mantenere nel tempo una carica elettrica.

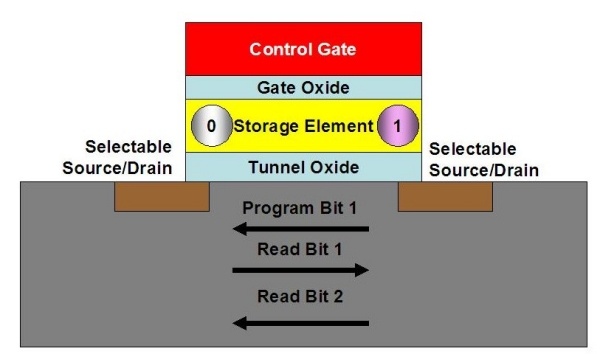

Figura 16: schema di una cella NAND 1-bit con charge trap

Analogamente a quanto già indicato in precedenza riguardo la differenza tra gate flottanti a singolo o multilivello, anche nel caso dei charge trap non cambia sostanzialmente il discorso: ciò sta a significare che all'origine di questa tecnologia era previsto l'uso di solo un livello di tensione mentre, allo stato attuale, i charge trap adottati nelle 3D Vertical sono tipicamente multilivello a quattro tensioni e permettono quindi di combinare l'uso di due bit.

Il necessario strato destinato al trasporto dei segnali viene pertanto costituito da un foglio non conduttivo posto planarmente e ricoperto in superficie da uno strato conduttivo polisiliconico.

Il principio costruttivo delle 3D V-NAND prevede la sovrapposizione di svariati strati costituiti fondamentalmente da Ossido di Silicio, isolati l'un l'altro da relativi fogli non conduttivi.

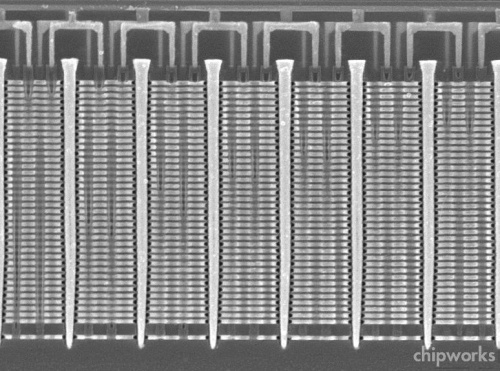

Figura 17: un array di Flash V-NAND al microscopio elettronico (fonte Chipworks)

Per implementare questa soluzione gli ingegneri rispolverarono una tecnica d'avanguardia, adottata oltre una decina di anni prima da Fujitsu e qualche anno dopo applicata in più larga scala su particolari memorie Flash NOR: le cosiddette MirrorBit del produttore americano di semiconduttori Spansion.

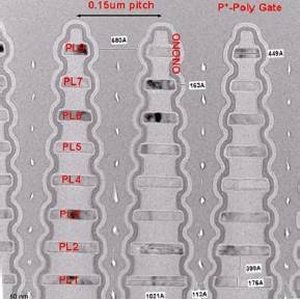

Questa tecnologia prevede che i gate di controllo sulla stringa planare siano interconnessi ai charge trap tramite un opportuno canale di comunicazione, il quale segue in questo modo uno sviluppo verticale: sia Toshiba che Samsung per raggiungere 128Gbit nella prima generazione di 3D V-NAND utilizzarono un pattern verticale da 24 strati, divenuti 32 nell'attuale seconda generazione.

Figura 18: una serie di V-NAND al microscopio elettronico (fonte Spansion)

Per quanto riguarda la seconda generazione del produttore coreano, quella attualmente in commercio, a fronte di un corposo incremento del 33% utile ad incrementare la densità di memorizzazione, sembrerebbe invece che questi ulteriori layer possibilmente non siano stati usati come spazio di memorizzazione aggiuntivo, ma che Samsung abbia voluto mantenere la densità di 128Gbit scegliendo di adottare un'impronta planare più snella, in modo da liberare in qualche modo le wordline verticali dall'insorgere di indesiderate interferenze elettriche che con questa tecnologia possono instaurarsi tra celle contigue.