Toshiba e Western Digital stanno preparando delle nuove 3D NAND Flash ad alta densità passando da 96 a 128 strati.

Nella nomenclatura di Toshiba tali chip di memoria si chiameranno BiCS-5 e, contrariamente alle attese, nonostante l'elevata densità, si tratterà di NAND di tipo TLC (3 bit per cella) e non QLC (4 bit per cella), questo perché la resa produttiva di quest'ultima tecnologia è ancora troppo bassa.

Le BICS-5 saranno realizzate su quattro livelli rispetto ai canonici due delle attuali TLC con una capacità di 512Gb, il 33% in più rispetto alle NAND a 96 strati e potrebbero fare capolino già nel 2020 entrando in produzione di massa nel 2021.

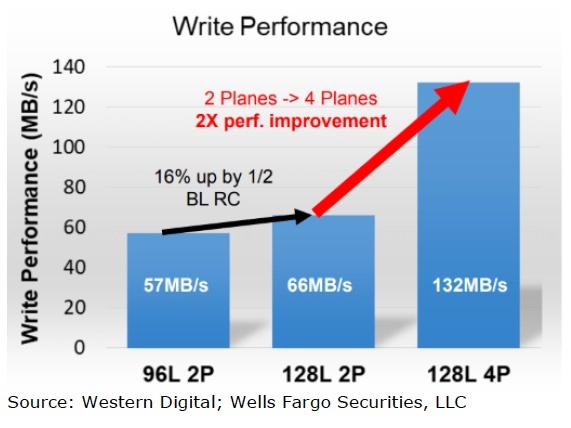

Tutti livelli sono accessibili in modo indipendente ed in parallelo il che si traduce in un raddoppio delle prestazioni in scrittura che passano da 66 a 132 MB/s.

Il die utilizza anche un design di tipo CuA (Circuitry-under-Array), un'innovazione progettuale in cui i circuiti logici si trovano nella parte più bassa, con strati di dati sovrapposti, comportando un risparmio del 15% nella dimensione dello stampo.

Secondo Aaron Rakers, un analista senior di Wells Fargo, il rendimento di Toshiba per wafer da 300mm potrebbe arrivare fino all'85%.

Allegati:

Fonte: Blocks & Files

Rispondi quotando

Rispondi quotando