1. DDR5 in pillole

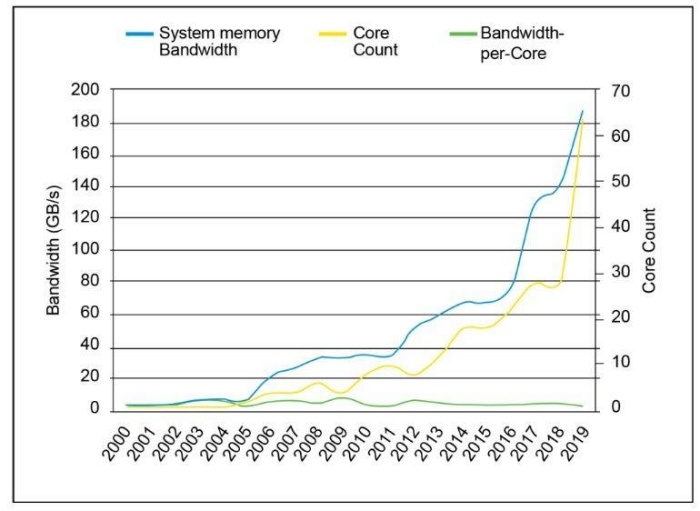

Inizialmente previsto per il 2018, lo standard DDR5 è stato rilasciato ufficialmente da JEDEC a luglio del 2020, debuttando di fatto sul mercato nel 2021 in occasione del lancio da parte di Intel della nuova piattaforma Alder Lake, per far fronte alle esigenze di banda richiesta dal crescente numero di core delle nuove CPU, specialmente in ambito server, come evidenziato nella tabella di seguito riportata.

Queste nuove memorie promettono sostanzialmente un miglioramento su tre fronti:

- incremento della velocità e della larghezza di banda;

- riduzione dei consumi;

- aumento della capacità per modulo.

| JEDEC DDR Generations | ||||||

| RAM type | DDR5 | DDR4 | DDR3 | LPDDR5 | ||

| Max Die Density | 64 Gbit | 16 Gbit | 4 Gbit | 32 Gbit | ||

| Max UDIMM Size (DSDR) | 128 GB | 32 GB | 8 GB | N/A | ||

| Max Data Rate | 6.4 Gbps | 3.2 Gbps | 1.6 Gbps | 6.4Gbps | ||

| Channels | 2 | 1 | 1 | 1 | ||

| Total Width (Non-ECC) | 64-bits (2x32-bit) | 64-bits | 64-bits | 16-bits | ||

| Banks (Per Group) | 4 | 4 | 8 | 16 | ||

| Bank Groups | 8/4 | 4/2 | 1 | 4 | ||

| Burst Length | BL16 | BL8 | BL8 | BL16 | ||

| Voltage (Vdd) | 1.1v | 1.2v | 1.5v | 1.05v | ||

| Vddq | 1.1v | 1.2v | 1.5v | 0.5v | ||

Maggiore velocitÃ

I primi moduli DDR5 ad essere commercializzati hanno frequenze di 4800MHz ed offrono quindi una banda più ampia del 50% rispetto a quella messa a disposizione da moduli DDR4 a 3200MHz.

Sono comunque già in commercio versioni da 5200 a oltre 6000MHz, che garantiscono una velocità di trasferimento teorica fino a 49,6 GB/s per singolo modulo.

I moduli DDR5 hanno un totale di 288 pin, lo stesso numero dei moduli DDR4, ma sono organizzati in modo diverso.

La posizione della "tacca" è differente con il preciso scopo di non rendere fisicamente compatibili gli slot tra i due standard.

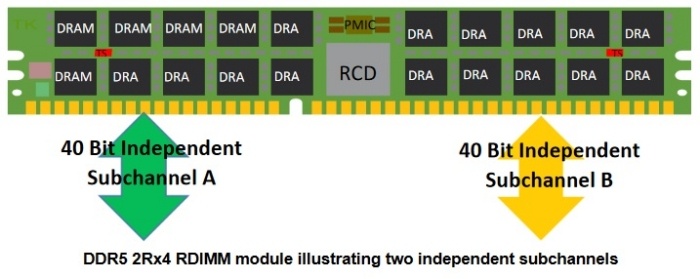

Sulle memorie DDR4 abbiamo un unico canale da 72 bit, composto da 64 bit per i dati ed eventuali 8 bit per la correzione degli errori (ECC).

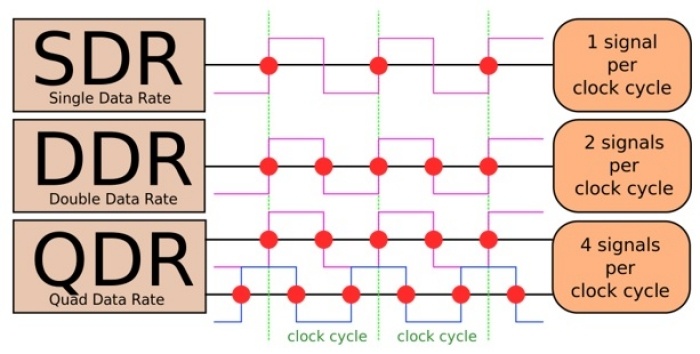

La frequenza a cui lavora il canale è quella per cui è stato progettato il modulo ed è la stessa sia per il trasferimento dei dati che per l'invio dei comandi, quindi per un modulo DDR4 da 3200MHz è di 1600MHz e la si dichiara doppia perché i moduli DDR, fin dalla loro introduzione, presentano la caratteristica di poter trasmettere dati sia sul fronte di salita che di discesa del clock.

Un modulo DDR4 da 3200MHz può quindi trasferire su ogni fronte del clock 8byte (64bit costituiti da 8 stringhe da 8 bit), motivo per cui la banda teorica messa a disposizione sarà quindi:

8byte (ampiezza bus) x 1600 x 106 (Hz) x 2 (DDR) = 25600 x 106 byte = 25,6 GB/s

I moduli DDR5 possono contare su due canali distinti da 40bit, di cui 32bit per i dati ed eventuali 8 bit per la correzione degli errori (ECC), ma la frequenza a cui vengono trasferiti i dati è doppia rispetto a quella di riferimento, per cui i moduli DDR5 4800MHz, hanno un clock base di 1200MHz ed un clock dati di 2400MHz.

La banda teorica messa a disposizione sarà quindi:

2 (subchannel) x 4byte (ampiezza bus) x 1200 x 106 (Hz) x 2 (clock doppio) x 2 (DDR) = 38400 x 106 byte = 38,4 GB/s

La velocità di trasmissione dati è ulteriormente migliorata rispetto alle DDR4 grazie alla riduzione dei tempi d'attesa per il refresh delle celle di memoria.

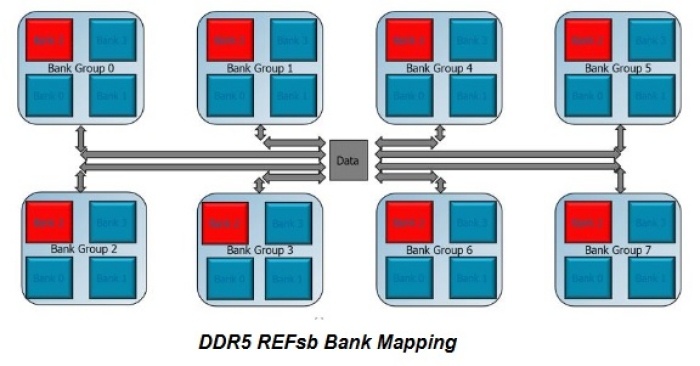

Ciclicamente è necessario ripristinare il livello di carica delle singole celle di memoria e questa operazione viene eseguita sulle DDR4 su tutti banchi richiedendo un certo tempo (desumibile dal valore del timing RFC); durante tale periodo nessuna operazione di lettura o scrittura è consentita.

Sui moduli DDR5 è possibile procedere al refresh come sulla precedente generazione (REFab) oppure solo su alcuni banchi (REFsb).

In questo modo i banchi non interessati dal refresh potranno continuare ad essere utilizzati: da sola questa tecnica dovrebbe apportare un beneficio in termini di prestazioni dal 6% al 9%.

Il burst lenght, ossia la quantità di dati che può essere trasferita tra il modulo di memoria e la CPU, raddoppia per le DDR5 arrivando a 16 contro gli 8 dei moduli DDR4.

In questo modo sarà possibile trasmettere 64byte (dimensione tipica dei registri in una CPU) per ogni burst utilizzando solo un sub-canale da 32bit, mentre per le DDR4 tale capacità viene raggiunta utilizzando tutti i 64bit a disposizione.

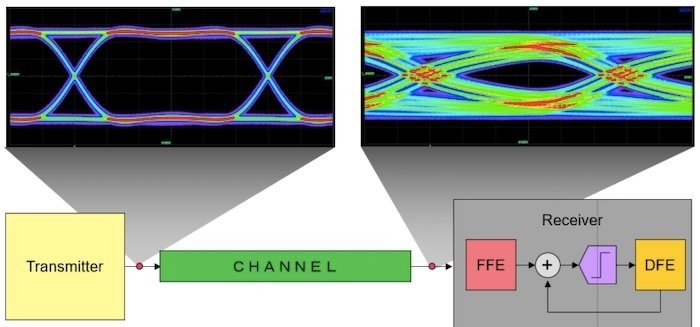

Al fine di ridurre l'alterazione del dato durante la trasmissione sul canale è stata aggiunta una nuova funzionalità , denominata DFE (Decision Feedback Equalization), che ha lo scopo di eliminare gli effetti del rumore durante la trasmissione dei dati sul canale.

Il canale è difatti costituito da sottili conduttori in rame che si comportano come un filtro passa basso: le componenti in alta frequenza del segnale vengono attenuate e ciò porta ad avere in uscita un segnale disturbato e meno nitido di quello trasmesso.

Ulteriori informazioni sull'argomento sono contenute a questo link.

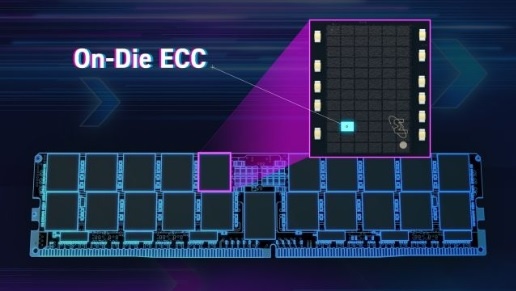

I moduli DDR5 implementano la correzione degli errori interni (On-Die ECC), mitigando il rischio di trasmettere dati corrotti.

L'espediente si è reso necessario per migliorare la resa del processo litografico al crescere della densità di dati archiviabili su ogni singolo chip.

Tale controllo viene effettuato prima di inviare il dato e non è quindi da confondere con l'ECC standard, che si occupa di correggere eventuali errori occorsi durante trasmissione del dato verso la CPU che si possono verificare sul canale.

Per tale funzione sono infatti sempre necessari pin aggiuntivi di ridondanza che devono essere letti dal controller; tale funzionalità resta quindi disponibile solo sui prodotti di classe server.

Riduzione dei consumi

La tensione operativa di 1,1V garantisce una consistente riduzione dell'energia consumata rispetto ai moduli DDR4 alimentati a 1,2V/1,35V.

Inoltre, diversamente dalle DDR4, i chip di memoria presenti sul modulo non sono alimentati dalla scheda madre, ma direttamente da un controller, denominato PMIC (Power Management Integrated Circuit), integrato su ogni DIMM.

La tensione di funzionamento viene generata a partire da quella da 12V per i moduli di classe server, mentre per i moduli destinati ai PC si attinge dalla linea da 5V.

La scelta di spostare la gestione dell'alimentazione sui singoli moduli sgrava la scheda madre da questo compito riducendone la complessità a livello di design.

Maggiore capacitÃ

I chip di memoria DDR4 hanno raggiunto una capacità limite di 2GB (16Gb), consentendo quindi la produzione di moduli da 32GB (16 chip da 2GB).

Al momento gli integrati disponibili presentano una capacità di 16 gigabit e, per tale motivo, il taglio minimo dei moduli DDR5 è di 16GB, con 8 chip da 16 gigabit su una sola faccia (single sided).

I chip DDR5 promettono tuttavia di arrivare fino ai 64Gb, il che potrebbe consentire la produzione di moduli mainstream fino a 128GB e addirittura 2TB per le versioni server.

Una delle soluzioni che consentirà di incrementare enormemente la densità delle memorie è quella di impilare un maggior numero di strati.