Nehalem sarà il capostipite della futura architettura Intel che andrà a rimpiazzare l'architettura Core e la sua naturale evoluzione Enhanced Core.

Nehalem Die

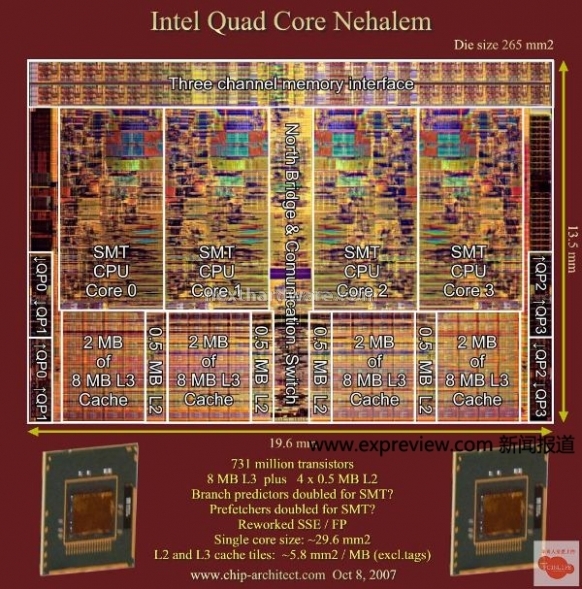

Come si vede dall'immagine, avrà un memory controller integrato. La novità e che sembra essere a 3 canali, in modo da poter ampliare la banda passante utilizzando tre o sei moduli. Ci saranno 8 MB di cache L3 complessivi, non è chiaro se condiviso o meno tra i vari core (da come è strutturato il die sembrerebbe di no), più ci saranno 512 KB di cache L2 dedicati a ciascun core.

Ai lati ci sono i circuiti che metteranno in comunicazione i 4 core con le restanti periferiche sulla scheda madre via FSB.

Ogni core probabilmente avrà i circuiti che si occupano del Branch Prediction e del Prefetch delle istruzioni raddoppiate poiché ciascun core dovrebbe essere in grado di elaborare 2 thread contemporaneamente, in una sorta di ritorno all'Hyper Threading. Non ci sono ancora informazioni però su come è strutturata la pipeline di ciascun core.

Nehalem sarà costruito a 45 nm, e questo permetterà di contenere notevolmente le dimensioni del die. Facendo un confronto con R600 (chip totalmente diverso, ma ha grossomodo la stessa quantità di transistor con processo produttivo a 80 nm), siamo a 265 mm 2 contro i 420 mm 2.

Quindi Intel sembra aver messo molta carne al fuoco. Vedremo Nehalem in azione nel 2008 inoltrato.

Rispondi quotando

Rispondi quotando